产品分类

CST2314

CST2314 是一个使用CMOS 制程技术的四输入数字音质处理IC。

CST2314将音量(Volume)左右声道平衡(balance)、高低音质(Treble & Bass)、响度(Loudness)等控制及可选择增益入(selectable input gain)内建于单一芯片中,使得CST2314 具有高效能及高可靠度,且只需运用少许的外围组件,便可达高效率的音质处理功能。

CST2314 的所有功能均可藉由序列总线(I 2 C bus)的驱动来达成,并可将其程序化而达多变的功能。

CST2314将音量(Volume)左右声道平衡(balance)、高低音质(Treble & Bass)、响度(Loudness)等控制及可选择增益入(selectable input gain)内建于单一芯片中,使得CST2314 具有高效能及高可靠度,且只需运用少许的外围组件,便可达高效率的音质处理功能。

CST2314 的所有功能均可藉由序列总线(I 2 C bus)的驱动来达成,并可将其程序化而达多变的功能。

CST2314概述:

CST2314 是一个使用CMOS 制程技术的四输入数字音质处理IC。

CST2314将音量(Volume)左右声道平衡(balance)、高低音质(Treble & Bass)、响度(Loudness)等控制及可选择增益入(selectable input gain)内建于单一芯片中,使得CST2314 具有高效能及高可靠度,且只需运用少许的外围组件,便可达高效率的音质处理功能。

CST2314 的所有功能均可藉由序列总线(I 2 C bus)的驱动来达成,并可将其程序化而达多变的功能。

CST2314的脚位功能和应 用电路是利于作PCB 布局的简易化,并能为相关音响应用节省成本。

CST2314提供SOP28封装。CST2314特性:

简化外部组件

高低音控制

响度控制

可选择4 个立体声的增益输入

可降低外部噪声的输入/输出系统

可左右平衡的2 个独立扬声器控制

独立静音功能

音量控制每阶为1.25dB

低失真

低直流准位漂移

可由微处理机序列总线I2C 接口控制

CST2314提供SOP28封装

CST2314应用:

汽车音响

立体声音效系统(Hi-Fi Audio System)

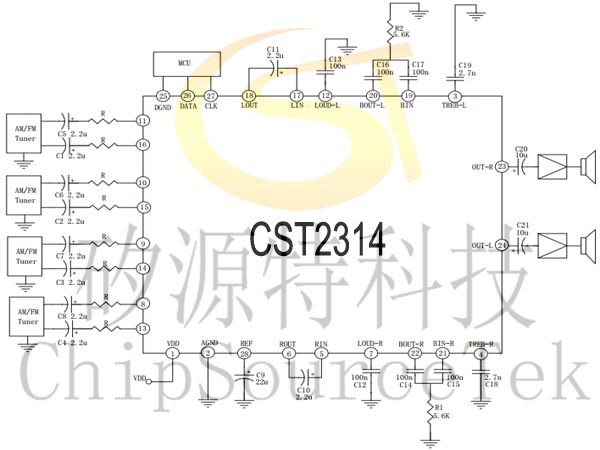

CST2314应用电路图:

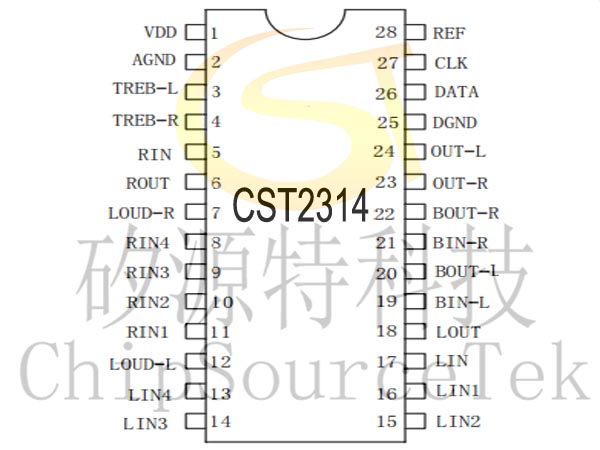

CST2314引脚分布:

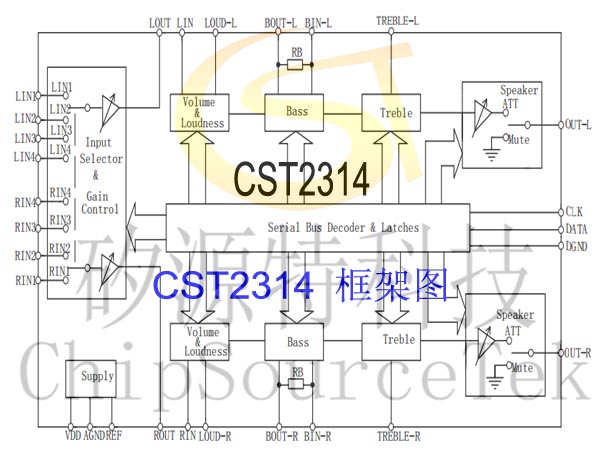

CST2314框架图:

CST2314封装图:

CST2314功能叙述

序列汇流排介面( I 2 C Bus Interface )

籍由使用DATA和CLK汇流排,可使CST2314于微处理机间做资料的传输。因此,DATA和CLK便构成此序列汇流排介面。

资料确认( Data Validity )

当CLK讯号是在“高准位”时,DATALine上的资料才会被视为正确且稳定的资料。而只有当CLK讯号在“低准位”时,DATA Line才可做高、低准位的切换。

开始和结束(start and stop conditions )

当(1)CLK讯号设定在高准位,且

(2)DATA讯号由高准位转换成低准位时;则表示序列资料的“开始”。

当(1)CLK讯号设定在高准位,且

(2)DATA讯号由低准位转换成高准位时;则表示序列资料的“结束”。

位元组格式( Byte format )

每一个传输到DATA Line 位元组(byte)有八个位元(bit),每一位元组后面需有一“认可”位元,且以最大符号位元(MSB)为首的方式传送出去。

“ 认可 ” 信号( Acknowledge )

在第九个时脉时主体(微处理机)先将DATA Line 设定为电阻性的高准位,若周边设备(CST2314)认可此信号,则DATALine 将会被周边设备(CST2314)拉至低准位,使DATALine 在此时脉中保持一定稳定的抵准位状态。

这个已被定址的音质处理器(CST2314)在收到每一位元组(BYTE)后,即产生一“认可”的动作;否则在第九个时脉(CLOCK)的时间内Data Line 将会一直保持着高准位状态。

无 “ 认可 ” 信号的传输( Transmission without Acknowledge )

如果您想省略此音质处理器(CST2314)对“认可”信号的侦测,可使用一较简单的传输方法。其方式为CST2314在收到每一位元组(byte)后,等待一时脉(clock),不做时脉的确认。如果您使用此种方法,将会有较大的机会造成传输错误,并且会减低对杂讯的免疫力。

介面协定( Interface Protocol )

介面协定包含:

1.开始(start)条件

2.包含有CST2314的位址(address)位元组。此位元组的第八个位元须为“0”。如此CST2314才可确认此CST2314的位址位元组已经结束。

3.一资料序列(N个位元组+认可位元)。

4.结束(stop)条件。

控制资料( Data Byte )的格式( Software Specification )

CST2314位址(address)